FPGAによるアクセラレーションのメリット

カスタム・アクセラレータ開発

CPU処理の限界に直面しているお客様へ。

お客様のアプリケーションに特化したカスタムアクセラレータで、飛躍的な性能向上を実現します。画像処理、通信制御、科学技術計算など、お客様のニーズに合わせたカスタムアクセラレータを開発し、CPUでは困難なスループットをFPGAで実現いたします。

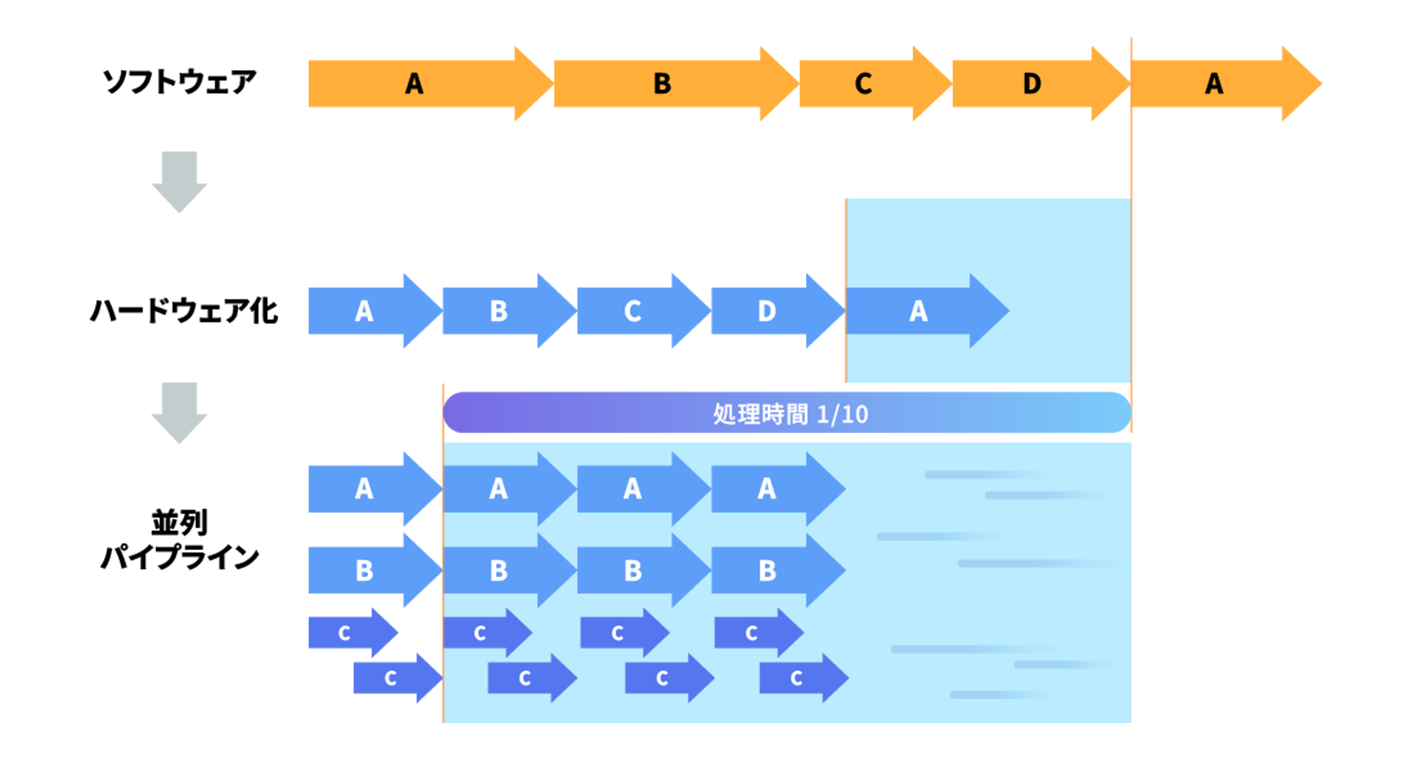

FPGAで実施することのメリット

リアルタイム性が求められるシステム開発のお客様へ。

FPGAの並列処理能力により、CPUでは不可能な超高速データ処理を実現します。FPGAはパイプライン処理や並列処理をハードウェアレベルで実装できるため、リアルタイム性が求められる画像処理や、大量のデータ処理が必要な科学技術計算などの分野で、飛躍的な性能向上を実現いたします。

システム性能の担保

処理時間の確定性や開発期間の短縮を求めるお客様へ。

経験豊富なハードウェアエンジニアが演算レイテンシを最適化したアーキテクチャを設計し、システム性能を保証します。ハードウェア演算により処理時間が固定(揺らぎなし)され、システム性能(仕様)が担保されます。これにより、開発時に発生するジッタの影響(過負荷による想定外の処理遅延やマージンの設計など)から解放されます。

Altera Solution Acceleration Partner

信頼と実績のパートナーシップ。

当社は Altera Solution Acceleration Partner (ASAP)

です。Altera社のFPGAに関する深い知識と豊富な開発経験を活かし、お客様に最適なソリューションを提供します。

Lattice Partner Network

信頼と実績のパートナーシップ。

当社はFPGAに関する深い知識と豊富な開発経験を活かし、お客様に最適なソリューションを提供します。