IEEE754 準拠 32bit 浮動小数点演算ユニット

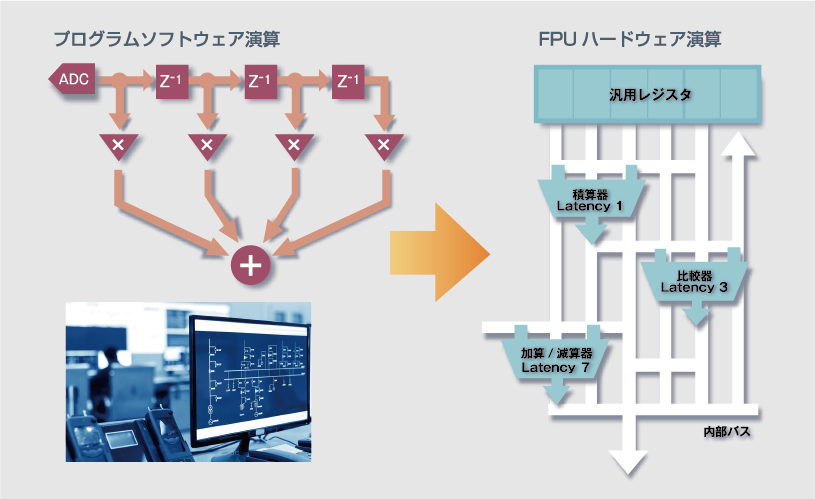

浮動小数点 FIR 演算回路を FPGA で実装し、既存のC ソースからのアルゴリズムの高速化を 行いました。 本ユニットは、お客様設計の FPGA に IP として採用されています。

ハード設計

FPGA 設計

研究機器/設備

開発内容

- FPGA で任意周波 浮動小数点 FIR 演算回路を FPGA で実装し、既存の C ソース

からのアルゴリズムの高速化 - 本ユニットは、お客様設計の FPGA に IP として採用

特徴

- IEEE754 32bit に準拠した浮動小数点演算ユニットを搭載

- 従来の C 言語による演算式を高速で実行できるように特別にカスタマイズされた高性能なパイプライン構造

- 小容量、低速 CLK で実行し、なおかつ、規定時間に終わるよう構造の最適化を実現