EtherCAT Master Products & Development Services

FPGA EtherCAT Master IP (Hardware Master)

For customers who want to achieve ultra-high-speed control on the order of

microseconds.

Our FPGA EtherCAT Master IP solves your challenges with

deterministic real-time performance and reduced CPU load.

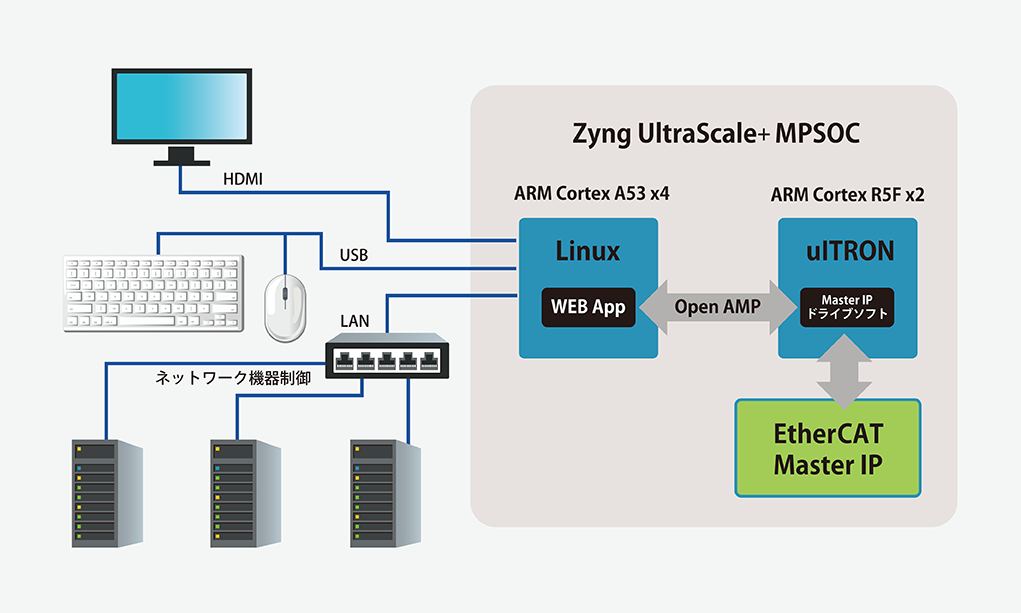

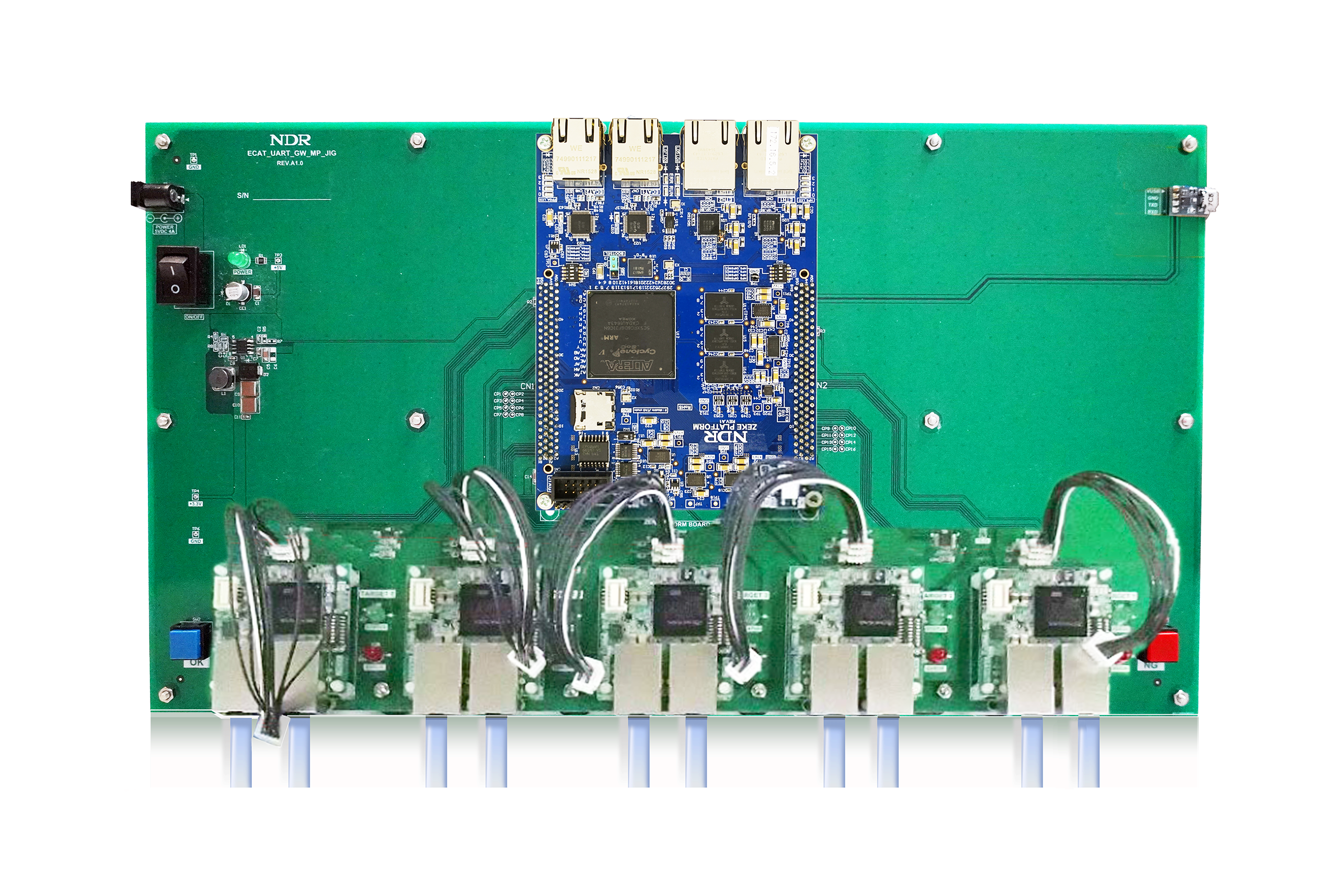

This is a hardware IP compatible with Altera/AMD FPGAs. By processing the EtherCAT master protocol

on the FPGA, it significantly reduces CPU load and achieves high-speed, high-precision communication

on the order of microseconds.

Key Features

- Improved main application performance by reducing CPU load

- Stable communication cycle with low jitter

- High-precision time synchronization (Distributed Clock) support (Pro version)

- Redundancy function support (Pro version)

- API and sample software included

Open-Source EtherCAT Master Solutions

For customers who want a flexible EtherCAT master with low cost.

Achieve

rapid implementation and custom development by leveraging open source.

We build an EtherCAT master in a Linux environment using open-source software. This is a low-cost

solution ideal for evaluation, implementation consideration, and technology acquisition. We will

port it to your board as a custom development.

Key Features

- Open-source environment with Linux and SOEM

- Hardware support through our BSP development service

- Low-cost EtherCAT master environment construction