EtherCAT マスター製品紹介・開発サービス

FPGA EtherCAT マスターIP(ハードウェアマスター)

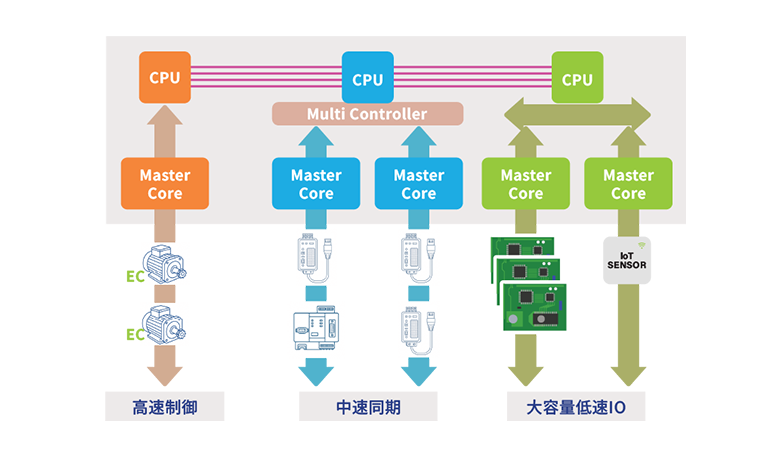

μsオーダーの超高速制御を実現したいお客様へ。

FPGA EtherCAT

マスターIPが、確定的なリアルタイム性能とCPU負荷軽減で、お客様の課題を解決します。

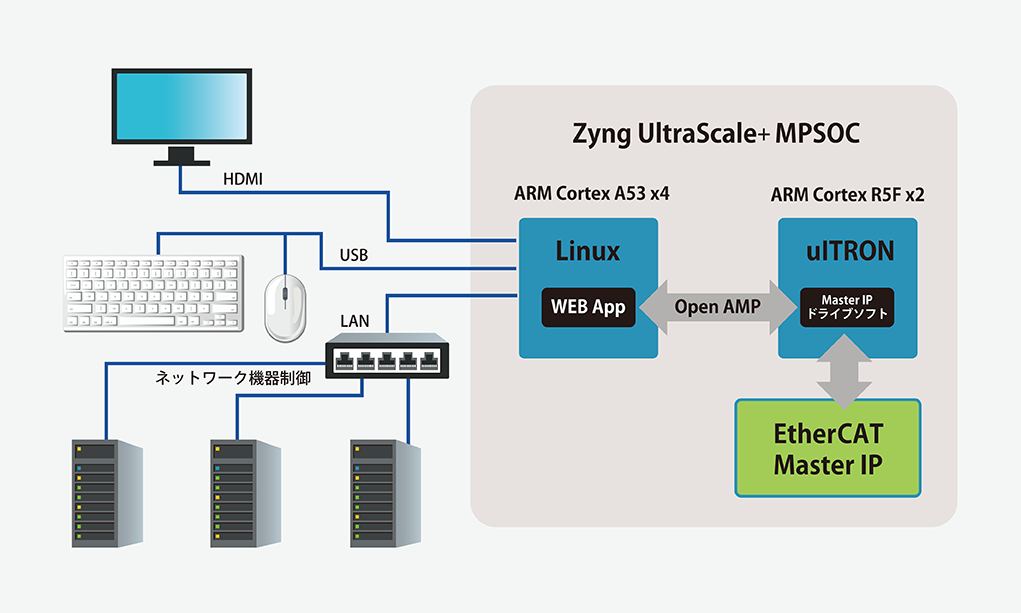

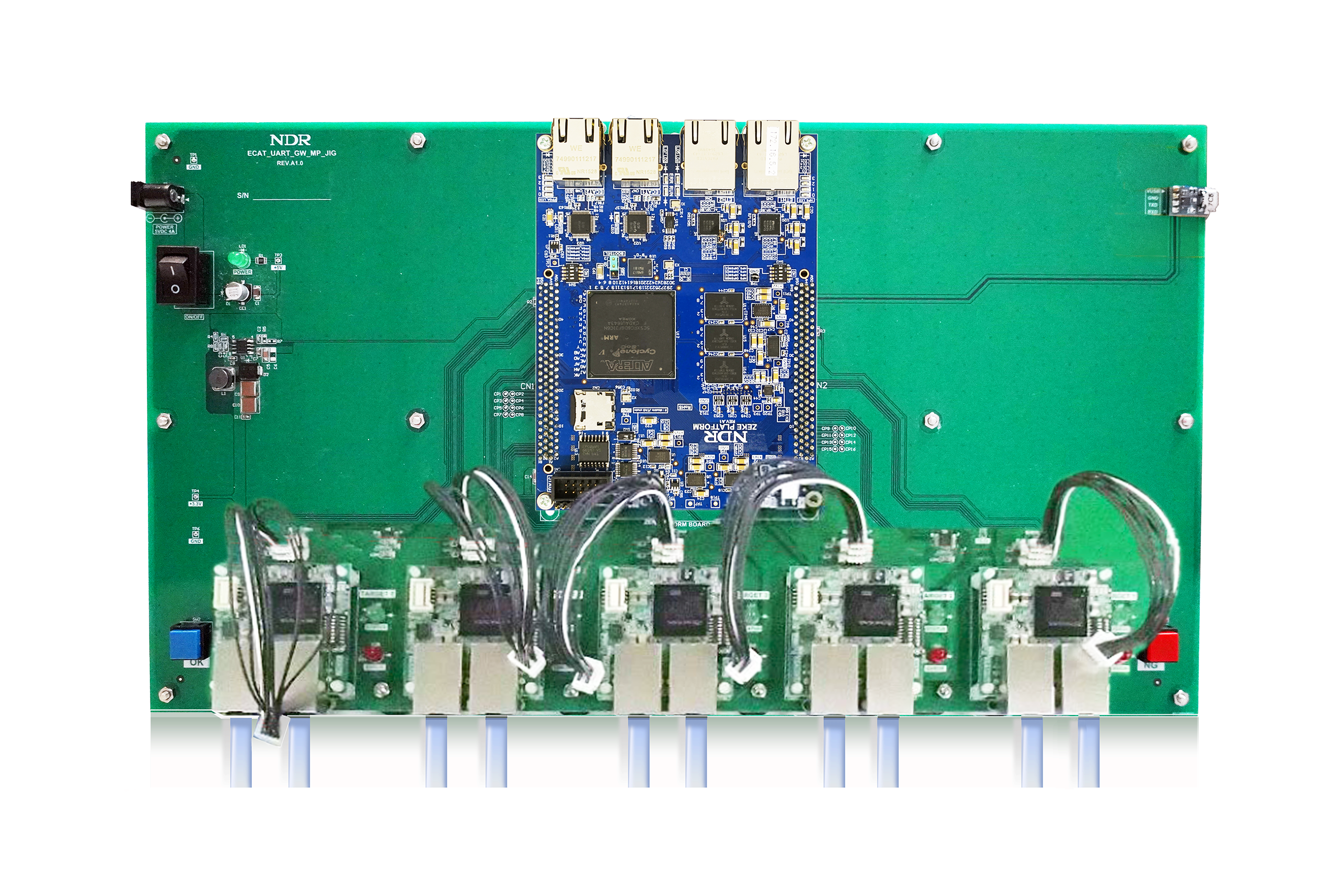

Altera/AMD

FPGAに対応したハードウェアIPです。EtherCATマスタープロトコルをFPGAで処理することで、CPU負荷を大幅に軽減し、μsオーダーの高速・高精度な通信を実現します。

主な特長

- CPU負荷軽減によるメインアプリケーションの性能向上

- ジッタの少ない安定した通信サイクル

- 高精度時刻同期 (Distributed Clock) 対応 (Pro版)

- 冗長化機能対応 (Pro版)

- APIとサンプルソフトウェア付属

オープンソースEtherCATマスターソリューション

コストを抑え、柔軟性の高いEtherCATマスターを求めるお客様へ。

オープンソース活用で、迅速な導入とカスタム開発を実現します。

オープンソースソフトウェアを活用し、Linux環境でEtherCATマスターを構築します。評価や導入検討、技術習得に最適な低コストソリューションです。カスタム開発としてお客様の基板にポーティングいたします。

主な特長

- LinuxとSOEMによるオープンソース環境

- BSP開発サービスによるハードウェア対応

- コストを抑えたEtherCATマスター環境構築