N-EMB-110

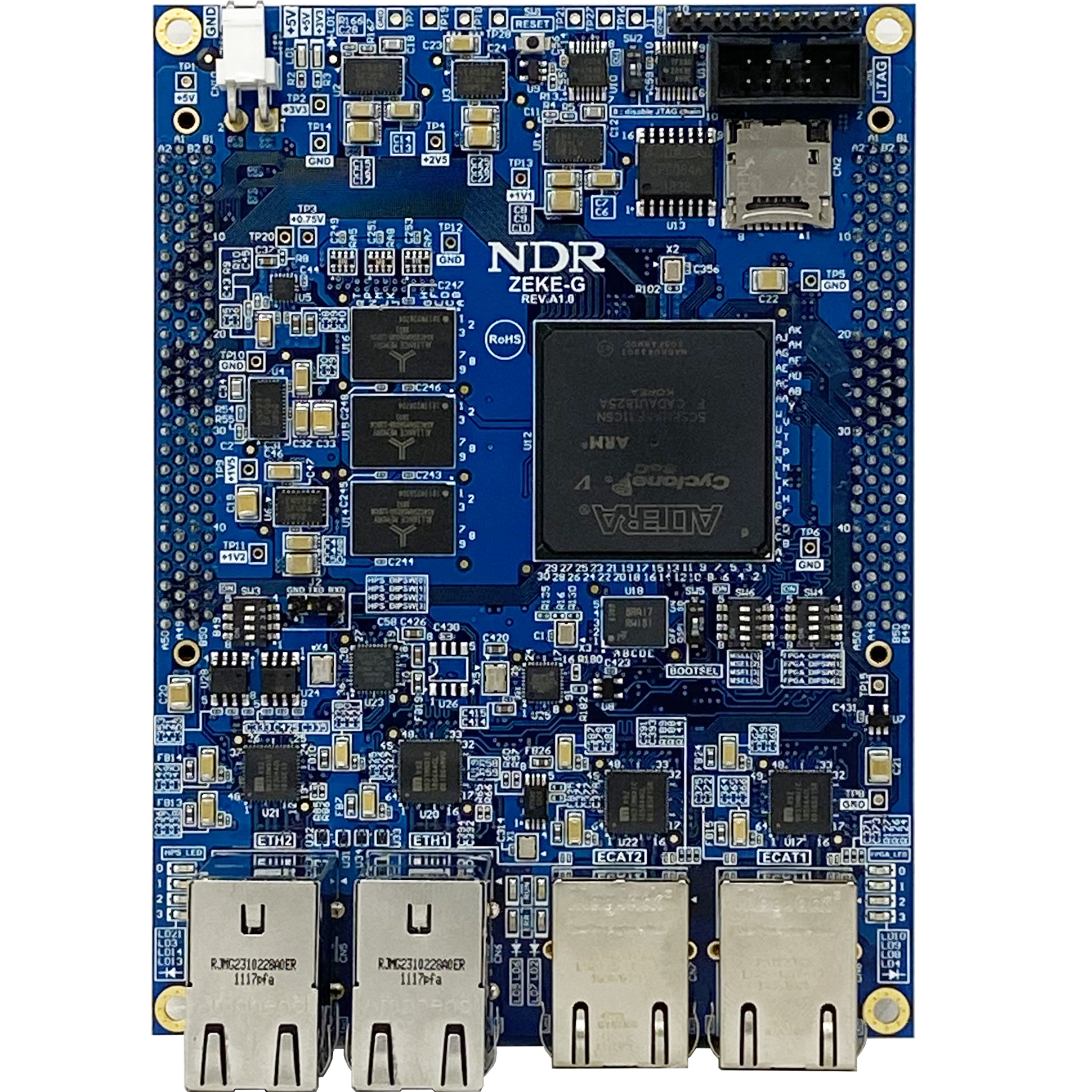

Intel Cyclone V SoC を搭載した高性能産業機器向けプラットフォーム

商品コード: EB-ZEKE-001-1

カテゴリー: EtherCAT Master, EtherCAT Slave, FPGA, エンベデッド

タグ: A9, Arm, Cortex, EtherCAT, FPGA

| モデル | 説明 | 価格 (税込) | |

|---|---|---|---|

| N-EMB-110-Pl |

プラットフォーム基板のみ OS 未搭載 |

¥237,600 | ログインへ |

| N-EMB-110-Pl-L |

N-EMB-110-PI に Xenomai Linux を搭載 |

¥237,600 | ログインへ |

| N-EMB-110-Pl-u |

N-EMB-110-PI に uC3 を搭載 |

¥237,600 | ログインへ |

| N-EMB-110-HM-L |

N-EMB-110-PI にハードウェアマスタ Xenomai Linux を搭載 |

¥237,600 | ログインへ |

| N-EMB-110-HM-u |

N-EMB-110-PI にハードウェアマスタ uC3 を搭載 |

¥237,600 | ログインへ |

説明

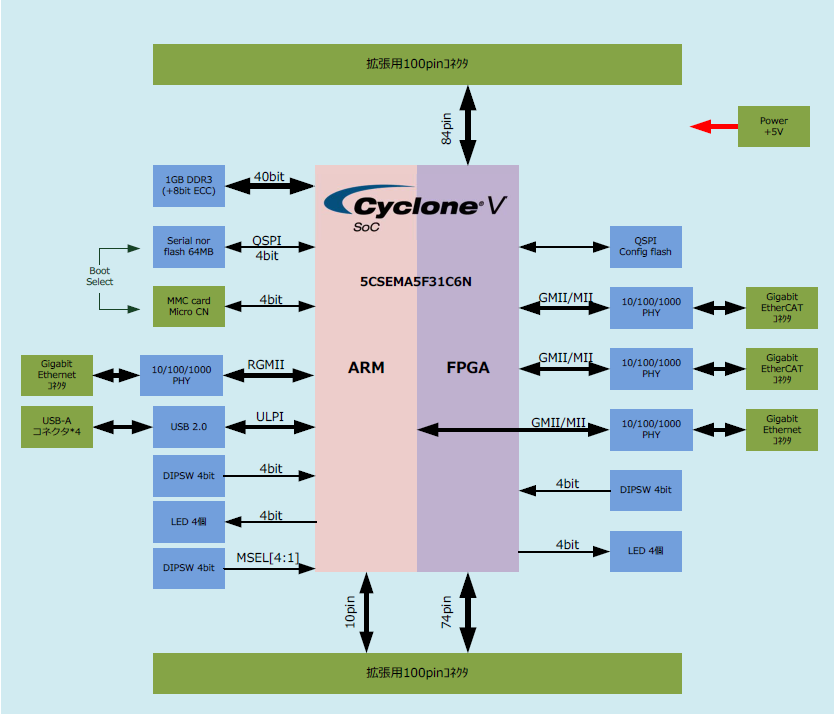

N-EMB-110 Platform は主に産業用イーサネット分野向けに開発されたプラットフォームです。

- Arm Cortex A9 x2 @925MHzを搭載した高性能CPUボード Linux等をSMPモードで使用することが出来ます。

- Arm のGbit EtherNET ポートが2ポート、USBとも使用可能な唯一のポートです。

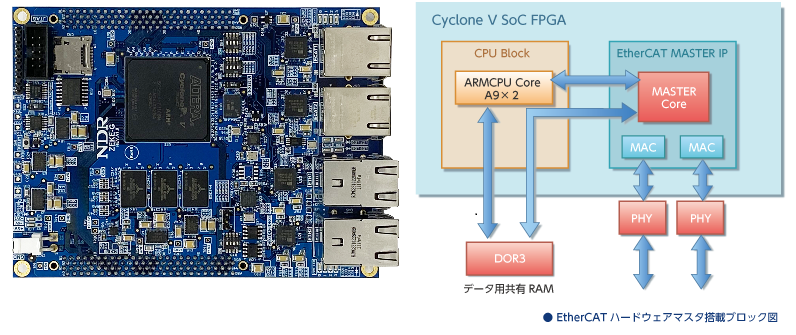

- FPGA に2つの 10/100/1000 PHY を搭載しているので、Intel 社のTSE MAC 等を使用することが可能です。

EtherCAT 対応

- ハードウェアマスタ FPGA側イーサネットを使用して、弊社のハードウェアマスタの 評価を行うことが可能です。

- ソフトウェアマスタ Arm側のイーサネットを使用して、各社有償ソフトウェアマスタを実装することが可能です。またオープンソースのマスタスタックを実装したデモ環境もご提供できます。

- スレーブ FPGA 側イーサネットは BECKOFF 社製 EtherCAT スレーブ IP 等を実装して、スレーブとしても使用できます。

追加情報

| 付属品 | |

|---|---|

| N-EMB-110-Pl | 回路図、部品リスト、パターン図 |

| ユーザーズマニュアル | |

| FPGA サンプルプロジェクト | |

| 電源ケーブル | |

| N-EMB-110-Pl-L | 回路図、部品リスト、パターン図 |

| ユーザーズマニュアル | |

| FPGA サンプルプロジェクト | |

| 電源ケーブル | |

| Boot 環境 SD | |

| N-EMB-110-Pl-u | 回路図、部品リスト、パターン図 |

| ユーザーズマニュアル | |

| FPGA サンプルプロジェクト | |

| 電源ケーブル | |

| Boot 環境 SD | |

| N-EMB-110-HM-L | 回路図、部品リスト、パターン図 |

| ユーザーズマニュアル | |

| Master IP 仕様書 | |

| FPGA Master IP サンプルプロジェクト | |

| Master IP API 仕様書 | |

| サンプルアプリケーション説明書 | |

| 電源ケーブル | |

| Boot 環境 SD | |

| N-EMB-110-HM-u | 回路図、部品リスト、パターン図 |

| ユーザーズマニュアル | |

| Master IP 仕様書 | |

| FPGA Master IP サンプルプロジェクト | |

| Master IP API 仕様書 | |

| サンプルアプリケーション説明書 | |

| 電源ケーブル | |

| Boot 環境 SD | |

仕様

| コア仕様 | ||

|---|---|---|

| FPGA+SoC | Cyclone V シリーズ (デュアルコアArm Cortex-A9 925MHz) | 5CSEMA5F31C6N |

| Config flash | EPCQ64ASI16N | |

| 電 源 | 入力:5.0V | 電源コネクタ (B2P-VH) or 拡張コネクタより供給 |

| 出力:3.3V | 拡張コネクタより 3.3V 出力 (トレラントバッファ用電源として使用することを想定) | |

| クロック | 25MHz | 3 個 搭載 (Arm 用、FPGA 用、PHY 用各 1 個) |

| GPIO | 1.27 25x4 列千鳥コネクタ 2 個 | FX2C-100S-1.27DSA (ヒロセ電機) |

| 各コネクタ 84CH (合計 168CH) | CN4:FPGA 部 84CH、CN9:FPGA 部 74CH、HPS 部 10CH | |

| Ethernet | Gigabit Ethernet (2CH):HPS | CN5、PHY:KSZ9031RNXIC CN6、PHY:KSZ9031MNXIC |

| 100base Ethernet (2CH):FPGA | CN7、PHY:KSZ9031MNXIC CN8、PHY:KSZ9031MMXIC | |

| LED | POWER LED | 2 個 搭載 (5.0V、3.3V) |

| ユーザ LED | 8 個 搭載 (HPS:緑 4 個、FPGA:緑 4 個) | |

| EtherCAT 用 LED | HPS:RUN (緑 1 個) 、ERR (赤 1 個) 、FPGA:RUN (緑 1 個)、ERR (赤 1 個) | |

| DIP スイッチ | 4 連 3 個 搭載 | HPS:2 個 (SW3、SW6:MSEL[4:1]) 設定用 |

| FPGA:1 個 (SW4) | ||

| プッシュスイッチ | 1 個 搭載 | リセットスイッチ (SW1) |

| JTAG | コネクタ | 1 個 搭載 (CN1) |

| スライドスイッチ (SW2) により接続を FPGA のみまたは、FPGA+HPS を設定可能 | ||

| メモリ | DDR3 | 256Mx32bit、8bit ECC 400MHz:AS4256M16D3B-12BCN |

| QSPI flash | 521Mbit (64Mx8bit) :MT25QL512ABB8E12-0SIT *1 | |

| マイクロ SD | マイクロ SD スロット (CN2) にカードを挿入しドライブとして使用 *2 | |

| *1 *2 ブートメモリとして使用可能、 SW5 にブートメモリを選択出来ます。 | ||