ZEKE Platform

High performance platform for industrial equipment powered by Cyclone V SoC

The ZEKE Platform is developed mainly for industrial Ethernet applications.

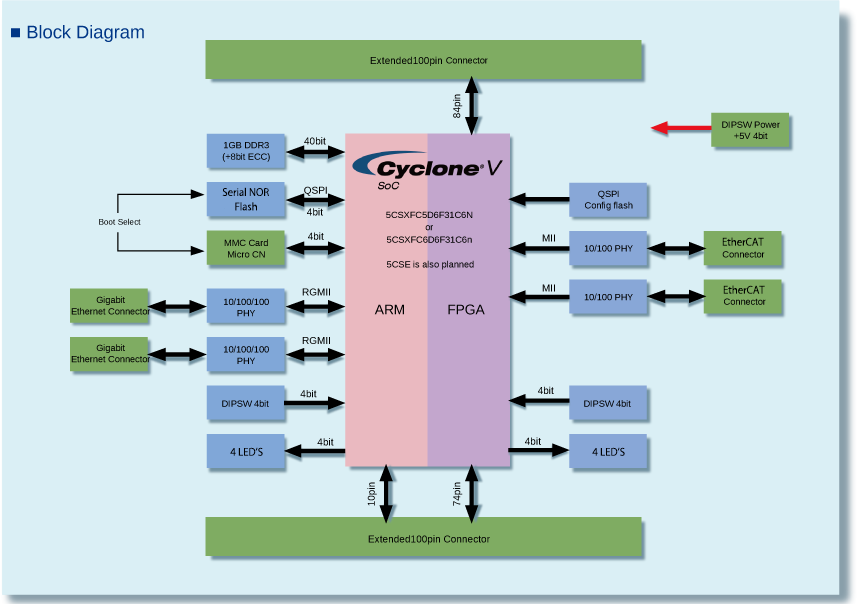

- ARM Cortex A9 x2 @925MHz High performance CPU board Linux etc., can be used in SMP mode.

- ZEKE is the only board, in which both the ARM Gbit Ethernet ports can be used.

- Since two 10/100 PHYs are implemented in the FPGA, TSE MAC from Intel Corporation can be used.

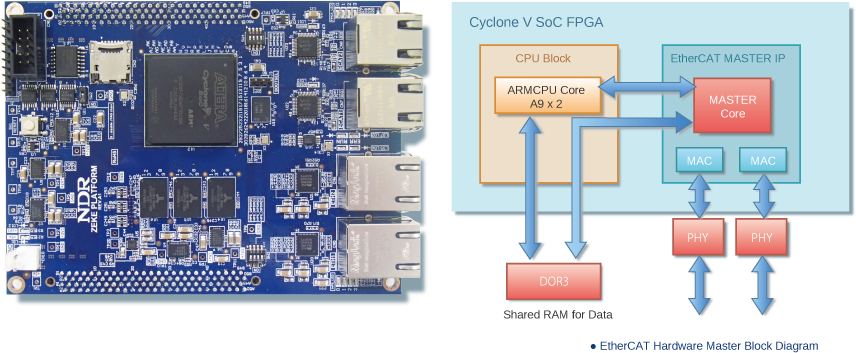

EtherCAT Implementation

- Hardware Master

Hardware Master can be evaluated with the FPGA’s Ethernet - Software Master

It is possible to implement paid software masters from various companies using the ethernet of the ARM. We also provide the demo environment for implementing the Open source Master stack. - Slave

Ethernet of the FPGA can also be used as a slave by implementing BECKHOFF EtherCAT slave IP etc.

Specifications

| Core Specification | ||

|---|---|---|

| FPGA+SoC | Cyclone V series (Dual core ARM Cortex-A 9 925MHz) | 5CSXFC6D6F31C6N/5CSXFC5D6F31C6N |

| 5CSXFC6D6F31C6N/5CSXFC5D6F31C6N | ||

| Config flash | EPCQ64ASI16N | |

| Power supply | Input: 5.0V | Supplied from power connector (B2P-VH) or extension connector |

| Output: 3.3V | 3.3V output from an extension connector (assumed to be used as a power supply for a tolerant buffer) | |

| Clock | 25MHz | 3 Units mounted (1 for each block (ARM, FPGA, PHY)) |

| GPIO | 2 No.s of 1.27 25x4 rows of staggered connectors | FX2C-100S-1.27DSA (Hirose Electric) |

| Each connector with 84CH (Total 168CH) | CN4: FPGA unit 84CH, CN9: FPGA unit 74CH, HPS unit 10CH | |

| Ethernet | Gigabit Ethernet (2CH):HPS | CN5, CN6 PHYKSZ9021RNI |

| 100base Ethernet (2CH):FPGA | CN7, CN8 PHY: TLK110PTR | |

| LED | POWER LED | 2 units (5.0V, 3.3V) |

| USER LED | 8 units (HPS: 4 green units, FPGA: 4 green units) | |

| EtherCAT LED | HPS: RUN (1 green unit), ERR (1 red unit), FPGA: RUN (1 green unit), ERR (1 red unit) | |

| DIP Switch | 2 out of 4 units loaded | HPS: 1 unit (SW3), FPGA: 1 unit (SW4) |

| Push switch | 1 unit | Reset switch (SW1) |

| JTAG | Connector | 1 unit (CN1) |

| Can be set to FPGA only or FPGA+HPS using the Slide switch (SW2) | ||

| Memory | DDR3 | 256Mx32bit, 8bit ECC 400MHz: AS4C256M16D3A-12BCN |

| QSPI flash | 521Mbit (64Mx8bit): MT25QL512ABB8E12-0SIT *1 | |

| Micro SD | Used as a driver by inserting the card into the MicroSD Slot (CN2) *2 | |

| *1 *2 Can be used as boot memory; boot memory can be selected by J3. | ||